https://tinyurl.com/y4srub3y

Drew Fustini (@pdp7)

<drew@beagleboard.org>

# \$ whoami

- Open Source Hardware designer at <u>OSH Park</u>

- PCB manufacturing service in the USA

- <drew@oshpark.com> | twitter: @oshpark

- Board of Directors, <u>BeagleBoard.org Foundation</u>

- BeagleBone is a small open source hardware Linux computer

- <drew@beagleboard.org>

- Board of Directors, <u>Open Source Hardware Association (OSHWA)</u>

- o OSHW Certification Program: <a href="https://certification.oshwa.org/">https://certification.oshwa.org/</a>

- RISC-V Ambassador for RISC-V International

- https://riscv.org/risc-v-ambassadors/

### RISC-V (virtual) meetups around the world

#### **Munich RISC-V Group**

- München, Germany

- 359 members · Public group @

- Organized by Flo W. and 1 other

#### **Bay Area RISC-V Group**

- ( ) San Jose, CA

- 2, 1,197 members · Public group @

- Organized by Celeste Cooper and 4 others

Find many more at: <a href="https://riscv.org/local/">https://riscv.org/local/</a>

### **Upcoming Events**

- RISC-V (Virtual) Summit 2020

- December 8th to 10th

- https://tmt.knect365.com/risc-v-summit/

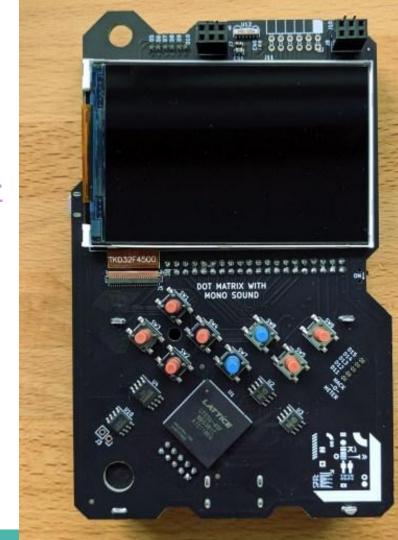

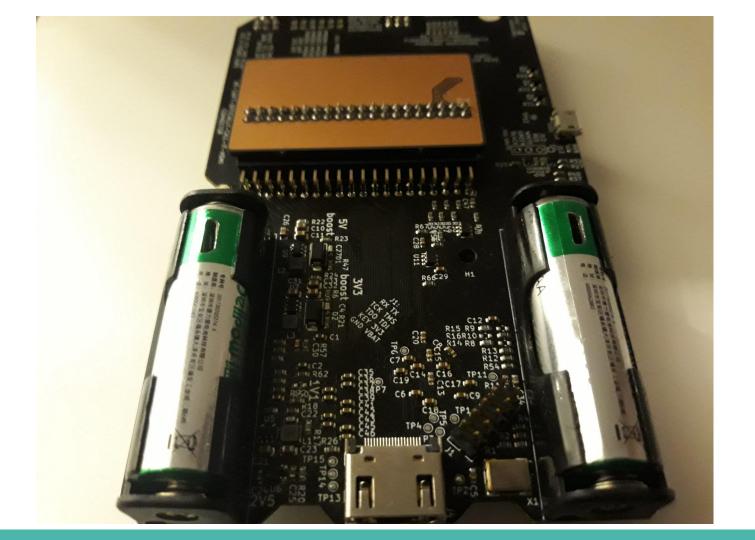

### MNT Reform by MNT Research GmbH

The open source DIY laptop for hacking, customization, and privacy

# Open Source Hardware

Hardware whose **design** is made **publicly available** so that anyone can **study**, **modify**, **distribute**, **make**, and **sell** the design or hardware based on that design

(source: Open Source Hardware (OSHW) Statement of Principles 1.0)

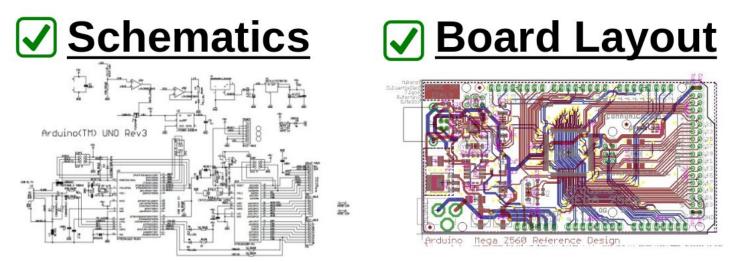

#### Documentation <u>required</u> for electronics:

Editable source files for CAD software such as KiCad or EAGLE

# **☑** Bill of Materials (BoM)

Not strict requirement, but best practice is for all components available from distributors in **low quantity**

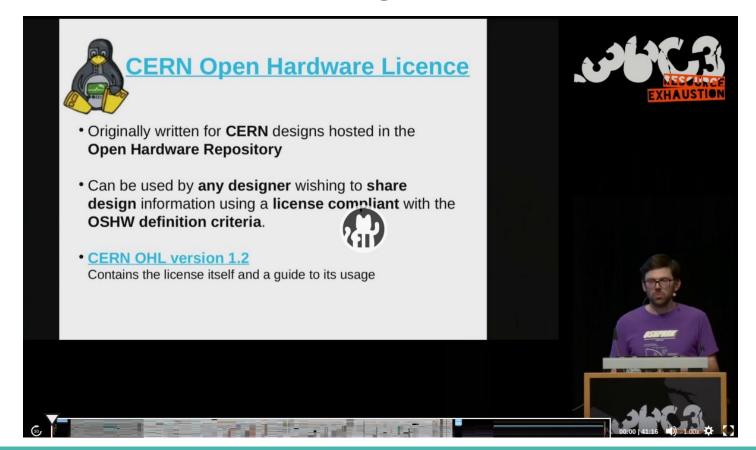

#### <u>Linux on Open Source Hardware with Open Source chip design</u>

Chaos Communication Congress (36c3), December 2019

# **Instruction Set Architecture (ISA)**

- Interface between hardware and software

- C++ program is compiled into instructions for a microprocessor (CPU) to execute.

- How does compiler know what instructions the CPU understands?

- This is defined by the Instruction Set Architecture

- ISA is a standard

- o a set of rules that define the tasks the processor can perform

- proprietary ISA's like x86 and ARM require commercial licensing

# RISC-V: a Free and Open ISA

#### History

- Started in 2010 by computer architecture researchers at UC Berkeley

- Watch the <u>RISC-V State of the Union</u> by Krste Asanovic

#### Why "RISC"?

RISC = Reduced Instruction Set Computer

#### Why "V"?

5th RISC instruction set to come of out UC Berkeley

#### Why is it "Free and Open"?

Specifications licensed as Creative Commons Attribution 4.0 International

### What is different about RISC-V?

#### Simple, clean-slate design

- Far smaller than other commercial ISAs

- Clear separation between unprivileged and privileged ISA

- Avoids micro-architecture or technology dependent features

#### Modular ISA designed for extensibility and specialization

- Small standard base, with multiple standard extensions

- Suitable for everything from tiny microcontrollers to supercomputers

#### Stable

- Base and standard extensions are frozen

- Additions via optional extensions, not new versions of base ISA

(source: Instruction Sets Want to be Free (Krste Asanović))

# **RISC-V Base Integer ISA**

RV321: 32-bit

less than 50 instructions needed!

RV32E: 32-bit embedded

reduces register count from 32 to 16 for tiny microcontrollers

RV64I: 64-bit

RV128I: 128-bit

Future-proof for nonvolatile RAM capacity; benefits security research

|              | imm[31:12]       | rd    | 0110111  |              |         |  |

|--------------|------------------|-------|----------|--------------|---------|--|

|              | imm[31:12]       | rd    | 0010111  |              |         |  |

|              | n[20 10:1 11 19] | rd    | 1101111  |              |         |  |

| imm[11:0     |                  | rs1   | 000      | rd           | 1100111 |  |

| mm[12 10:5]  | rs2              | rs1   | 000      | imm[4:1 11]  | 1100011 |  |

| mm[12 10:5]  | rs2              | rs1   | 001      | imm[4:1 11]  | 1100011 |  |

| mm[12 10:5]  | rs2              | rs1   | 100      | imm[4:1 11]  | 1100011 |  |

| mm[12 10:5]  | rs2              | rs1   | 101      | imm[4:1 11]  | 1100011 |  |

| mm[12 10:5]  | rs2              | rs1   | 110      | imm[4:1 11]  | 1100011 |  |

| mm[12 10:5]  | rs2              | rs1   | 111      | imm[4:1 11]  | 1100011 |  |

| imm[11:0     |                  | rs1   | 000      | rd           | 0000011 |  |

| imm[11:0     | rs1              | 001   | rd       | 0000011      |         |  |

| imm[11:0     | rs1              | 010   | rd       | 0000011      |         |  |

| imm[11:0     | rs1              | 100   | rd       | 0000011      |         |  |

| imm[11:0     | rs1              | 101   | rd       | 0000011      |         |  |

| imm[11:5]    | rs1              | 000   | imm[4:0] | 0100011      |         |  |

| imm[11:5]    | mm[11:5] rs2     |       | 001      | imm[4:0]     | 0100011 |  |

| imm[11:5]    | rs2              | rs1   | 010      | imm[4:0]     | 0100011 |  |

| imm[11:0     | rs1              | 000   | rd       | 0010011      |         |  |

| imm[11:0     | rs1              | 010   | rd       | 0010011      |         |  |

| imm[11:0     | rs1              | 011   | rd       | 0010011      |         |  |

| imm[11:0     | rs1              | 100   | rd       | 0010011      |         |  |

| imm[11:0     | rs1              | 110   | rd       | 0010011      |         |  |

| imm[11:0     | rs1              | 111   | rd       | 0010011      |         |  |

| 0000000      | shamt            | rs1   | 001      | rd           | 0010011 |  |

| 0000000      | shamt            | rs1   | 101      | rd           | 0010011 |  |

| 0100000      | shamt            | rs1   | 101      | rd           | 0010011 |  |

| 0000000      | rs2              | rs1   | 000      | rd           | 0110011 |  |

| 0100000 rs2  |                  | rs1   | 000      | rd           | 0110011 |  |

| 0000000 rs2  |                  | rs1   | 001      | rd           | 0110011 |  |

| 0000000 rs2  |                  | rs1   | 010      | rd           | 0110011 |  |

| 0000000 rs2  |                  | rs1   | 011      | rd           | 0110011 |  |

| 0000000 rs2  |                  | rs1   | 100      | rd           | 0110011 |  |

| 0000000 rs2  |                  | rs1   | 101      | rd           | 0110011 |  |

| 0100000 rs2  |                  | rs1   | 101      | rd           | 0110011 |  |

| 0000000 rs2  |                  | rs1   | 110      | rd           | 0110011 |  |

| 0000000 rs2  |                  | rs1   | 111      | rd           | 0110011 |  |

| fm pred succ |                  | rs1   | 000      | rd           | 0001111 |  |

| 0000000000   |                  | 00000 | 000      | 00000 111001 |         |  |

| 000000000    | 00000            | 000   | 00000    | 1110011      |         |  |

(source: RISC-V Summit 2019: State of the Union)

### RISC-V base plus standard extensions

#### Standard extensions

- **M**: integer multiply/divide

- **A**: atomic memory operations

- **F, D, Q:** floating point, double-precision, quad-precision

- G: "general purpose" ISA, short-hand for IMAFD

- C: compressed instruction encoding to conserve memory and cache like ARM Thumb

- o Additions via optional extensions like Vector but not new versions of base ISA

- Linux distros like Debian and Fedora target RV64GC

- Frozen in 2014, ratified 2019, will be supported forever

#### RV32I / RV64I / RV128I + M, A, F, D, Q, C RISC-V "Green Card"

|                                                                          | VI- | 5C-V             |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                |                                       |                 |            |                                       |                                       |                   |                | RISC-V R                                 | erer               | rence      | Card           |

|--------------------------------------------------------------------------|-----|------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|---------------------------------------|-----------------|------------|---------------------------------------|---------------------------------------|-------------------|----------------|------------------------------------------|--------------------|------------|----------------|

| Base Integer Instructions (32   64   128) RV Privileged Instructions (32 |     |                  |                | (32   64   128                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | )              | 3 Optional FP Extensions: RV32{F D Q} |                 |            |                                       | Optional Compressed Instructions: RVC |                   |                |                                          |                    |            |                |

| ategory Name                                                             | Fmt | RV(32 6          | 4 128)I Base   | Category                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Name           | Fmt RV m                              | nemonic         |            | Category Name                         | Fmt                                   | $RV\{F D Q\}$ (   | (HP/SP,DP,QP)  | Category Name                            | Fm                 | t          | RVC            |

| oads Load Byte                                                           | I   | LB               | rd, ral, imm   | CSR Access                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Atomic R/W     | R CSRRV                               | v rd,cs         | r, rsl     | Load Load                             | I                                     | FL(W, D, Q)       | rd, rsl, imm   | Loads Load Wo                            | rd CL              | C.LW       | rd',rsl',imm   |

| Load Halfword                                                            | I   | LH               | rd, rsl, imm   | Atomic R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Read & Set Bit | R CSRRS                               | rd, cs          | r, rsl     | Store Store                           | 5                                     | FS(W, D, Q)       | rsl,rs2,imm    | Load Word                                | SP CI              | C.LWSP     | rd,imm         |

| Load Word                                                                | 1   | L[W[D[Q]         | rd, rsl, imm   | Atomic Rea                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ad & Clear Bit | R CSRR                                | rd, es          | r,rsl      | Arithmetic ADD                        | R                                     | FADD. (SIDIQ)     | rd, rs1, rs2   | Load Do                                  | ible CL            | C.LD       | rd', rsl', imn |

| Load Byte Unsigned                                                       | I   | LBU              | rd, rsl, imm   | Ator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | mic R/W Imm    | R CSRR                                | WI rd,cs        | r,imm      | SUBtract                              | R                                     | FSUB. (SIDIQ)     | rd, rs1, rs2   | Load Double                              | SP CI              | C.LWSP     | rd,imm         |

| Load Half Unsigned                                                       | 1   | L(H(W)D)U        | rd, rsl, imm   | Atomic Read 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | & Set Bit Imm  | R CSRR                                | II rd, cs       | r,imm      | MULtiply                              | R                                     | FMUL. (SID(Q)     | rd, rs1, rs2   | Load Q                                   | uad CL             | C.LQ       | rd',rsl',imm   |

| itores Store Byte                                                        | S   | SB               | rsl,rs2,imm    | Atomic Read & C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Clear Bit Imm  | R CSRR                                |                 | r,imm      | DIVide                                | R                                     | FDIV. [SIDIQ]     | rd, rsl, rs2   | Load Quad                                | SP CI              | C.LQSP     | rd,imm         |

| Store Halfword                                                           |     | SH               | rs1,rs2,imm    | Change Level                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Env. Call      | R ECALI                               |                 |            | SQuare RooT                           | R                                     | FSQRT. [S]D[O]    | rd, rs1        | Load Byte Unsig                          | ned CL             | C. LBU     | rd',rsl',imm   |

| Store Word                                                               | S   | S[W D Q]         | rsl,rs2,imm    | Environme                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | nt Breakpoint  | R EBREJ                               | kK              | - 1        | Mul-Add Multiply-ADI                  | R                                     | FMADD.{SIDIQ}     | rd,rsl,rs2,rs3 | Float Load V                             | ord CL             | C.FLW      | rd',rsl',im    |

| hifts Shift Left                                                         | R   | SLL( W D)        | rd, rs1, rs2   | Enviror                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | nment Return   | R ERET                                |                 |            |                                       |                                       | FMSUB.(SID(Q)     |                | Float Load Do                            | ible CL            | C.FLD      | rd',rsl',im    |

| Shift Left Immediate                                                     | 1   | SLLI (   W   D)  | rd, rsl, shamt | Trap Redirect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | t to Superviso | R MRTS                                |                 |            | Negative Multiply-SUBtract            | R                                     | FMMSUB. (S D Q)   | rd,rs1,rs2,rs3 | Float Load Word                          | SP CI              | C.FLWSP    | rd,imm         |

| Shift Right                                                              | R   | SRL[[W]D]        | rd, rs1, rs2   | Redirect Trap                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | to Hypervisor  | R MRTH                                |                 |            | Negative Multiply-ADD                 | R                                     | FMMADD. [SIDIQI   | rd,rs1,rs2,rs3 | Float Load Double                        | SP CI              | C.FLDSP    | rd,imm         |

| Shift Right Immediate                                                    | I   | SRLI     W   D   | rd, rs1, shamt | Hypervisor Trap                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | to Supervisor  | R HRTS                                |                 |            | Sign Inject SiGN source               | R                                     | FSGNJ. [SIDIQ]    | rd, rs1, rs2   | Stores Store Wo                          | rd CS              | c.sw       | rs1',rs2',1    |

| Shift Right Arithmetic                                                   |     |                  | rd, rs1, rs2   | Interrupt Wa                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                |                                       |                 |            | Negative SiGN source                  |                                       |                   |                | Store Word                               |                    |            | rs2,imm        |

| Shift Right Arith Imm                                                    | I   | SRAI     W   D } | rd, rsl, shamt | MMU Supe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ervisor FENCE  | R SFENC                               | CE.VM rsl       |            | Xor SiGN source                       | R                                     | FSGNJX.[5]D[Q]    | rd,rsl,rs2     | Store Do                                 | ible CS            | C.SD       | rs1',rs2',i    |

| rithmetic ADD                                                            | R   | ADD[[W]D]        | rd, rs1, rs2   | Optional                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Multiply-D     |                                       | ension: RV3     | 2 <i>M</i> | Min/Max MNimum                        | R                                     | FMIN. (SIDIQ)     | rd, rs1, rs2   | Store Double                             | SP CS              | SC.SDSP    | rs2,imm        |

| ADD Immediate                                                            | I   | ADDI[[WID]       | rd, ral, imm   | Category                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Name Fmt       | RV3                                   | 32M (Mult-Div)  |            | MAXimum                               | R                                     | FMAX.[SID]Q1      | rd, rsl, rs2   | Store Q                                  | uad CS             | C.SQ       | rs1', rs2', it |

| SUBtract                                                                 | R   | SUB( W D)        | rd, rs1, rs2   | Multiply N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | fultiply R     | MUL( W D)                             | rd, rsl, rs;    | 2          | Compare Compare Float                 | R                                     | FEQ. [SIDIQ]      | rd, rsl, rs2   | Store Quad                               | SP CS              | Sc.sosp    | rs2,imm        |

| Load Upper Imm                                                           | U   | LUI              | rd, imm        | MULtiply up:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | per Half R     | MULH                                  | rd, rsl, rs     | 2          | Compare Float <                       | R                                     | FLT. (SIDIQ)      | rd, rs1, rs2   | Float Store V                            | ord CS             | S C. FSW   | rd',ral',im    |

| Add Upper Imm to PC                                                      | U   |                  | rd, imm        | MULtiply Half Si                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ign/Uns R      | MULHSU                                | rd, rsl, rsl    | 2          | Compare Float ≤                       | R                                     | FLE.(S D Q)       | rd, rsl, rs2   | Float Store Dox                          | ble CS             | S C. FED   | rd', rsl', im  |

| ogical XOR                                                               | R   | XOR              | rd, rsl, rs2   | MULtiply upper h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Half Uns R     | MULHU                                 | rd, rsl, rsl    | 2          | Categorize Classify Typ               | R                                     | FCLASS. [SIDIO]   | rd, rsl        | Float Store Word                         | SP CS              | S C. FSWSP | rd,imm         |

| XOR Immediate                                                            | 1   | XORI             | rd, rsl, imm   | Divide                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | DIVide R       | DIVIONIDI                             | rd, rsl, rsl    | 2          | Move Move from Integer                | R                                     | FMV.S.X           | rd, rsl        | Float Store Double                       | SP CS              | SC. FEDSP  | rd,imm         |

| OR                                                                       | R   | OR               | rd, rsl, rs2   | DIVide Ur                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | nsigned R      | DIVU                                  | rd, rsl, rsl    | 2          | Move to Integer                       | R                                     | FMV.X.S           | rd, rsl        | Arithmetic Al                            | XD CR              | C.ADD      | rd, rsl        |

| OR Immediate                                                             | 1   | ORI              | rd.ral.imm     | RemainderRE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Mainder R      | REM( W D)                             |                 |            | Convert Convert from In               |                                       |                   | f rd, rsl      | ADD W                                    | ord CR             | C.ADDW     | rd',rs2'       |

| AND                                                                      | R   | AND              | rd, rsl, rs2   | REMainder Ur                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | nsigned R      | REMULTIWID                            | rd, rsl, rs     |            | Convert from Int Unsigned             |                                       |                   |                | ADD Immed                                | ate CI             | C.ADDI     | rd, imm        |