OpenIoT Summit Europe 2018

# Compartmentalization in IoT

Trusted Firmware M

Secure Partitioning

Miklos Balint Ken Liu Arm

# **Agenda**

The right level of security

Hardware support

Compartmentalization scenarios

Interaction between isolated components

# **Challenges in IoT**

### High volume, low cost, low power

- Microcontrollers

- Small die

- No MMU (single, physical address space)

- XIP Flash code

- Small SRAM

### Wide spectrum of use-cases

- Different threat models

- Scalable solutions

Holistic approach to IoT security needed

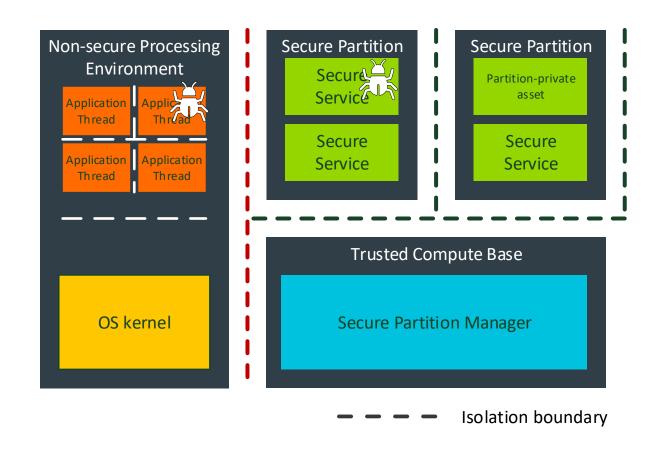

# Establishing the "right" level of security

#### Secure domain

Basic isolation – create a Secure Processing Environment

#### **Protected TCB**

Separate Root of Trust from Secure Partitions within SPE

#### Multiple tenancy in secure PE

More robustness – isolate all partitions from each other

#### **Non-Secure isolation**

Access policies for NS threads

### Hardware isolation

... the foundation for software security

### Physical isolation (e.g. dual-core system):

Dedicate cores/resources

Shared memory system or Mailbox

Concurrent execution

### Temporal isolation (e.g. Arm-v8M):

Privilege control – using MPU

Secure/Non-secure states (Secure Attribution)

Shared Processing Element, resources

# Interaction scenarios

### **Execution flows**

Crossing boundaries in single processing element

### Crossing from Non-secure to secure state

Non-secure thread requests secure service

### Isolated driver code

ISR execution in unprivileged partition

### Asynchronous events in non-secure PE

- Non-secure interrupt pre-empts secure operation

- Non-secure context awareness

- Concurrent secure service requests from non-secure threads

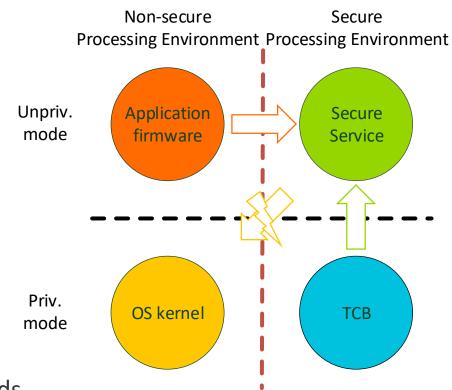

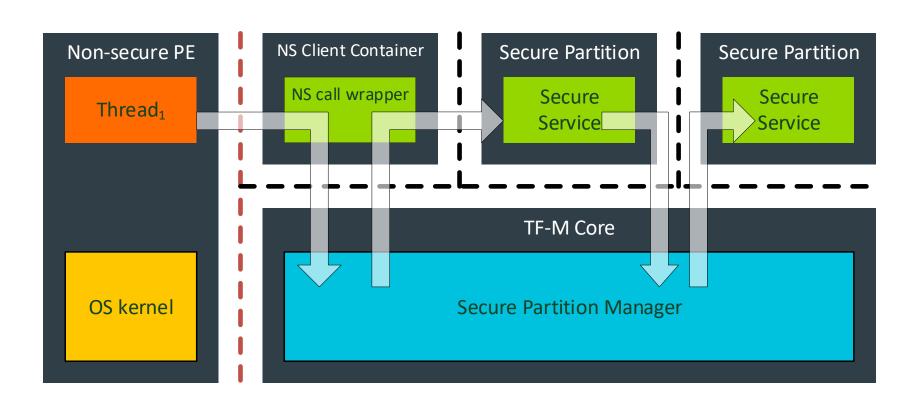

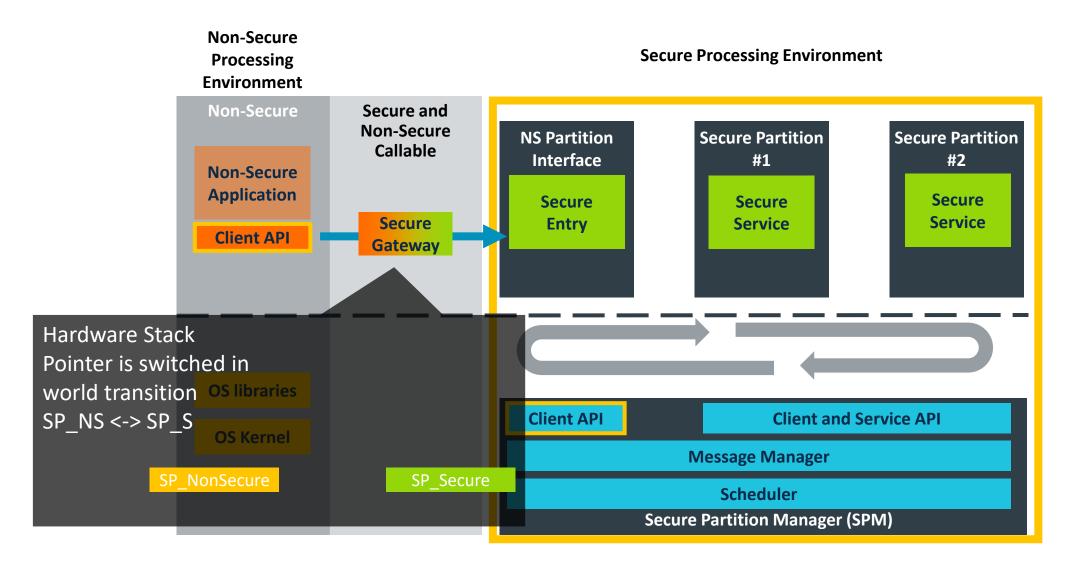

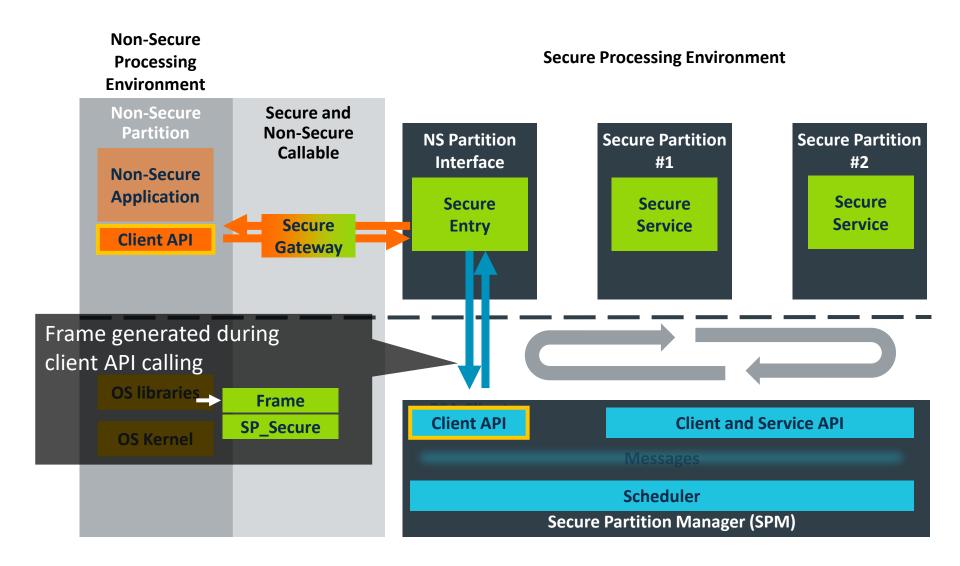

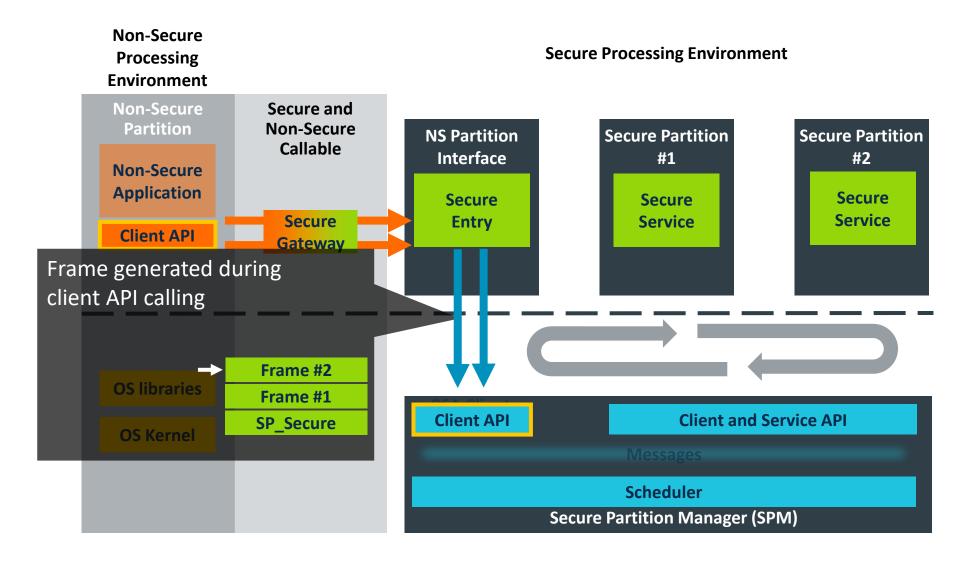

### Non-secure call to secure service

Security state change only permitted using dedicated entry points

Wrapper function triggers privileged management code

Secure Partition Management code

- Performs parameter sanitization

- Sets up Secure Partition (container)

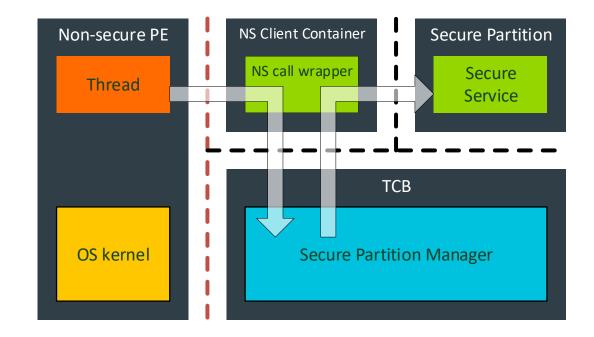

### Non-secure call to secure service

NS thread mode *Client*

S thread mode Wrapper code

S handler mode

Context management

S unprivileged thread Sandboxed context

NS thread

Secure veneer (NS Client ctx)

Secure Request SVC

Secure Service function

• Call Secure Service

Call Secure Request SVC Sanitize parameters

Save NS Client ctx

• Setup SP context

Perform secure service

NS thread

Secure veneer (NS Client ctx)

Secure Response SVC

Secure Service function

Continue execution

Return to NS

Save SP context

Restore NS Client context

Call Response handler

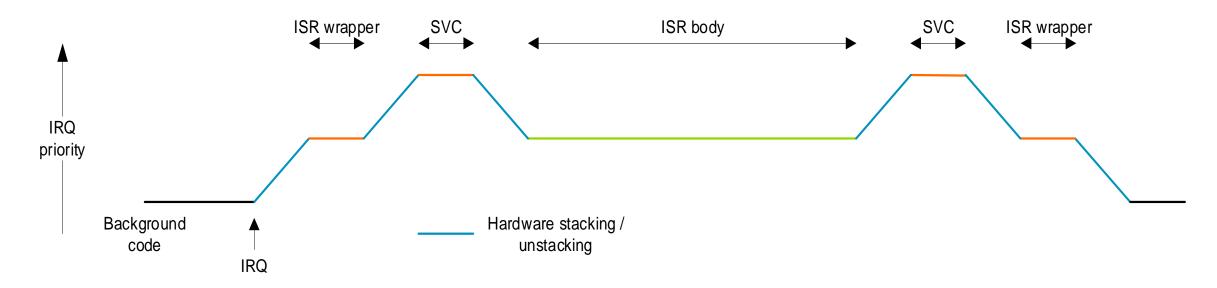

# Secure interrupt deprivileging

- Privileged ISR is wrapper

- Triggers Partition Manager

- Sandbox created

- Returns to thread mode

- Secure Partition code

- Executes deprivileged ISR

# Secure interrupt deprivileging

S handler mode S handler mode S unprivileged thread Original mode Original context Sandboxed context Wrapper code Context management **Secure Partition IRQ Request SVC Privileged ISR** Interrupted code **ISR**  Call IRQ request SVC Set up MPU sandbox Handle interrupt Gets interrupted Switch PSP • Ret. to unpriv. thread Secure Partition Interrupted code **Privileged ISR IRQ Done SVC ISR**  Continue execution Call IRQ Done SVC Return to original Restore MPU config, **PSP** state Return to priv. ISR Non-Confidential © Arm 2018

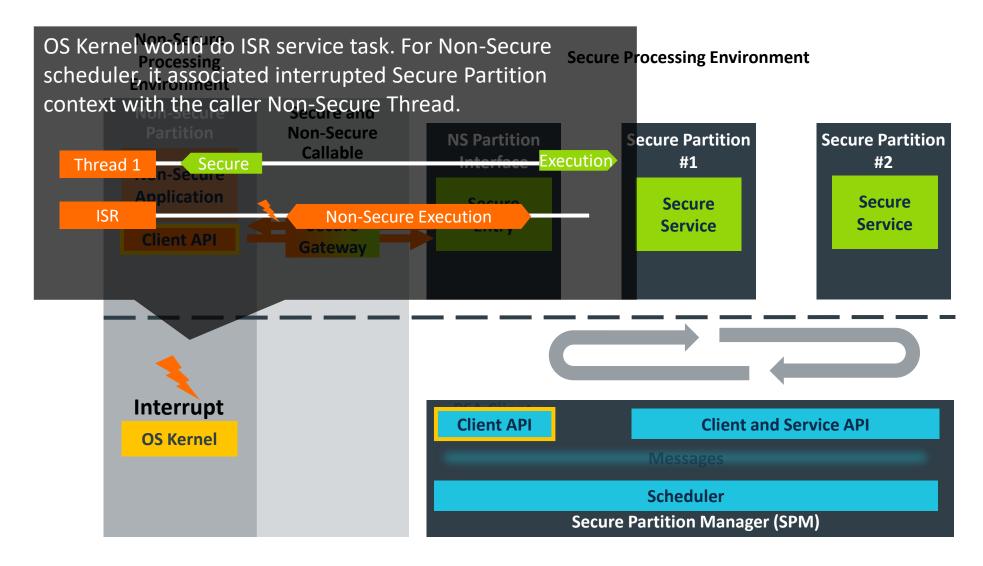

## **Non-Secure interrupts**

### Pre-emption of secure execution

Non-secure thread is executing

**Thread calls Secure Service**

Non-secure IRQ pre-empts operation

Secure context is stacked

Non-secure ISR is executed

Return from ISR resumes secure execution

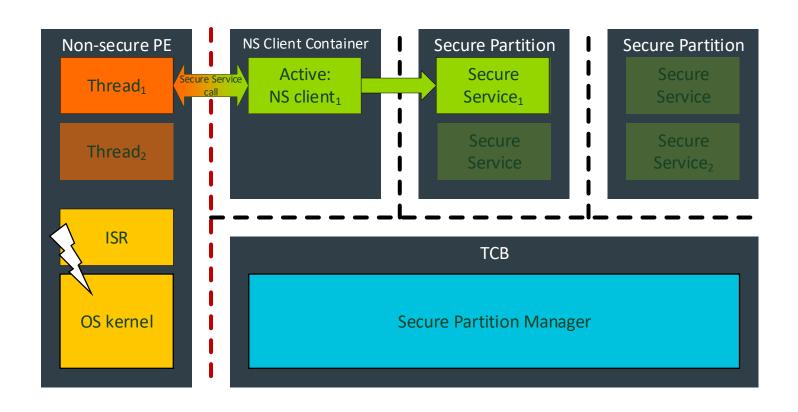

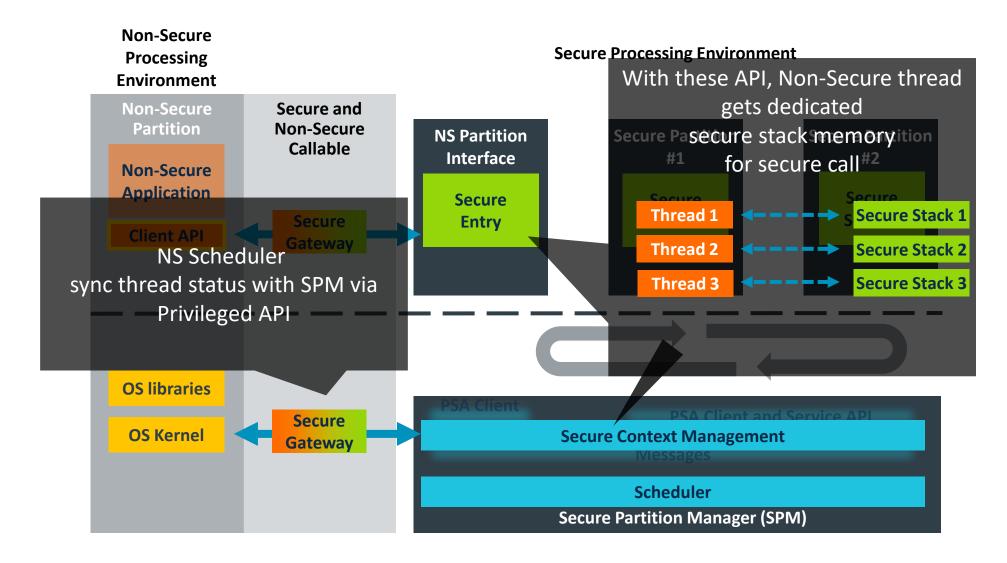

## **Context Management Functions**

### Non-secure context awareness in Arm-v8M

- 1. Non-secure threads created

- 2. Thread<sub>1</sub> calls Secure Service<sub>1</sub>

- 3. Non-secure IRQ pre-empts operation -> context change

- 4. Thread<sub>2</sub> calls secure service<sub>2</sub>

- 5. Secure service, returns

- 6. Thread, yields

- 7. Secure Service<sub>1</sub> returns

NS RTOS provides notification to SPM about context creation, deletion, load or store operation, enabling NS context-dependent access to secure assets/services.

# Implementations

# **Trusted Firmware M library model**

Secure Services implemented as functions

Arm-v8M architecture support

Secure Partition is a library of secure services

Synchronous execution of secure services

Programming model closely follows embedded/MCU concepts

Low footprint – on demand allocation of resources

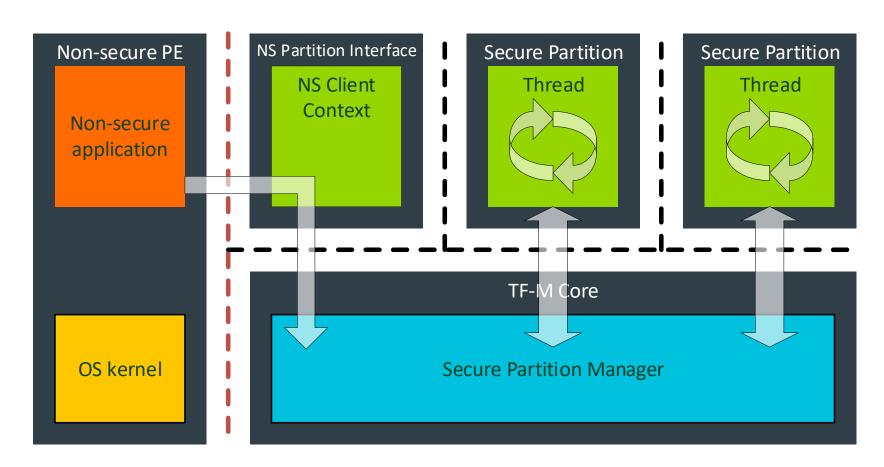

### **Trusted Firmware M thread model**

Secure Partitions implemented as threads

Connection/message based interaction

Robust, more prescriptive framework

Static allocation of secure resources

Asynchronous processing of service requests

Less architecture dependent -> well suited for physical separation

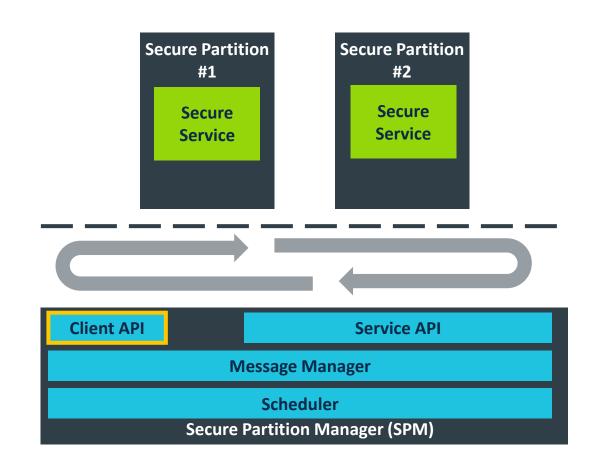

# Interaction with secure threads

# **TF-M Inter-Process Communication (IPC)**

- For TF-M Thread model

- Secure Partitions provide secure services

- NSPE is reflected as one Non-Secure Partition

- One thread in one Secure Partition

- While loop in thread waiting for messages

- Client call sent as messages

- Non-Secure Partition is a client.

- Secure Partition could be a client

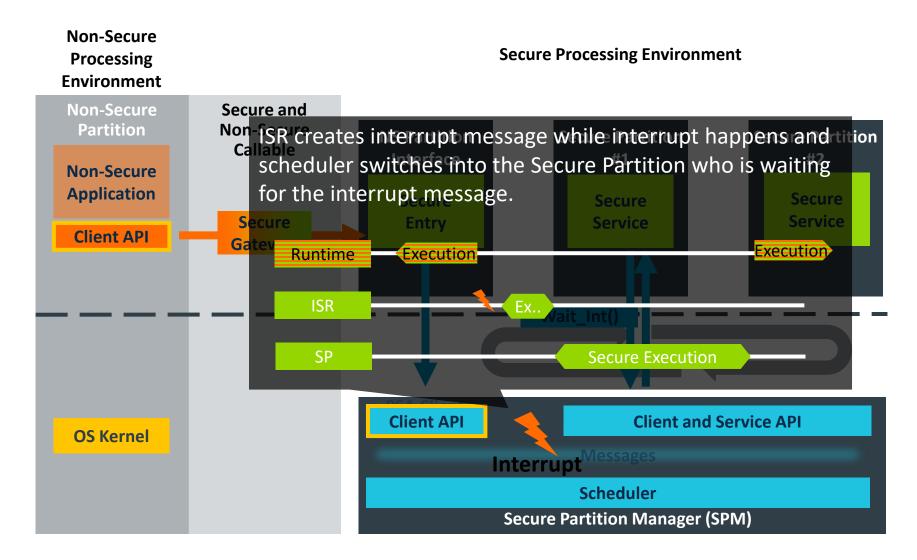

- Service Interrupt is handled asynchronously

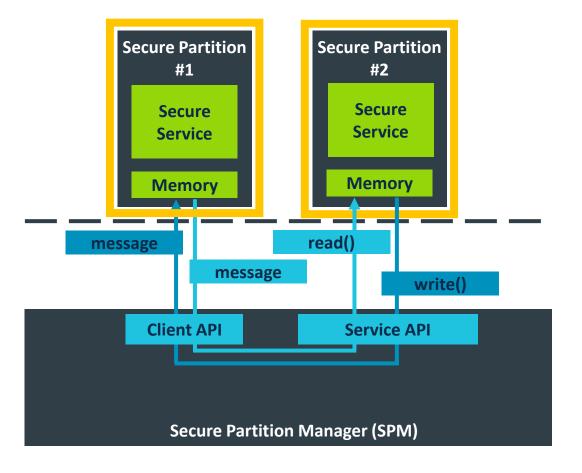

# **Security Consideration on Compartmentalization**

- No shared memory

- Streamed read/write APIs for copying memory

- Memory integrity checking based on isolation level

- Peripheral usage is also isolated

- Runtime protection rule change to isolate

## **Expand NSP with Arm-v8M TrustZone**

# **Single NS Thread requests Secure Service**

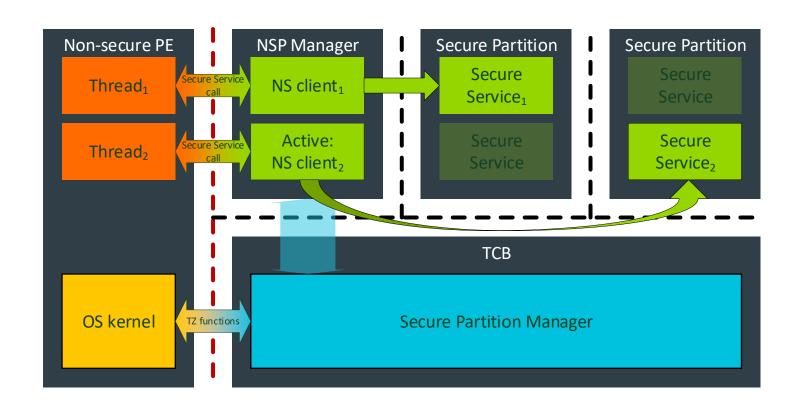

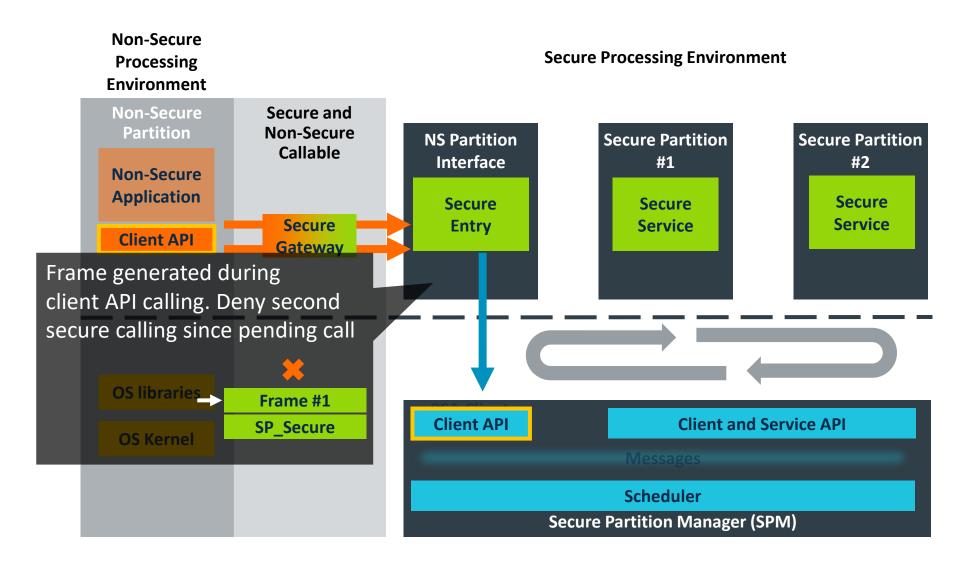

## Multiple NS Thread request Secure Service

### Multi-Thread NSPE Secure Call Solution 1

### Multi-Thread NSPE Secure Call Solution 2

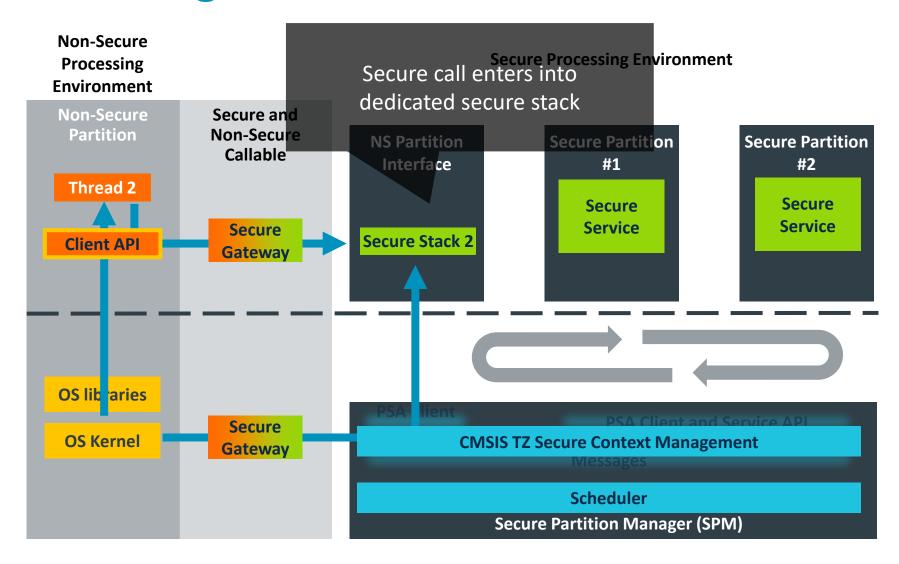

## **Solution 2 Calling Process**

## **Non-Secure Interrupt Preempts Secure Service**

### **Secure Interrupt Preempts Execution**

# Summary

# Compartmentalization in IoT – No one-size-fits-all

### Secure/non-secure isolation:

- physical

- temporal

### Privilege control:

- none

- within secure domain

- within non-secure domain

### Interaction:

- function calls

- IPC

- hardware mailbox

# How to get involved

TF-M is part of the Open Source/Open Governance trustedfirmware.org project

Code base: <a href="https://git.trustedfirmware.org/">https://git.trustedfirmware.org/</a>

TF-M Team @ OpenIoT Summit Europe 2018

- Shebu Kuriakose

- Ashutosh Singh

- Ken Liu

- Miklos Balint

### Get in touch

- Come round to the Arm booth during the summit

- Contact TF-M team at support-trustedfirmware@arm.com

More info on <u>developer.arm.com</u> and <u>trustedfirmware.org</u>

Thank You! Danke! Merci! 谢谢! ありがとう! **Gracias!** Kiitos! 감사합니다 धन्यवाद

# arm

The Arm trademarks featured in this presentation are registered trademarks or trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. All rights reserved. All other marks featured may be trademarks of their respective owners.

www.arm.com/company/policies/trademarks